The General Routing Table

The GRT is the largest part of Tritoncore-I. Some quick calculations put it at roughly twice the size of all the LUTs combined. The GRT is the reason Tritoncore-I would never be feasable for production, but nonetheless its design was integral to simplifying the programming enough to get the entire software stack complete within the six weeks we had.

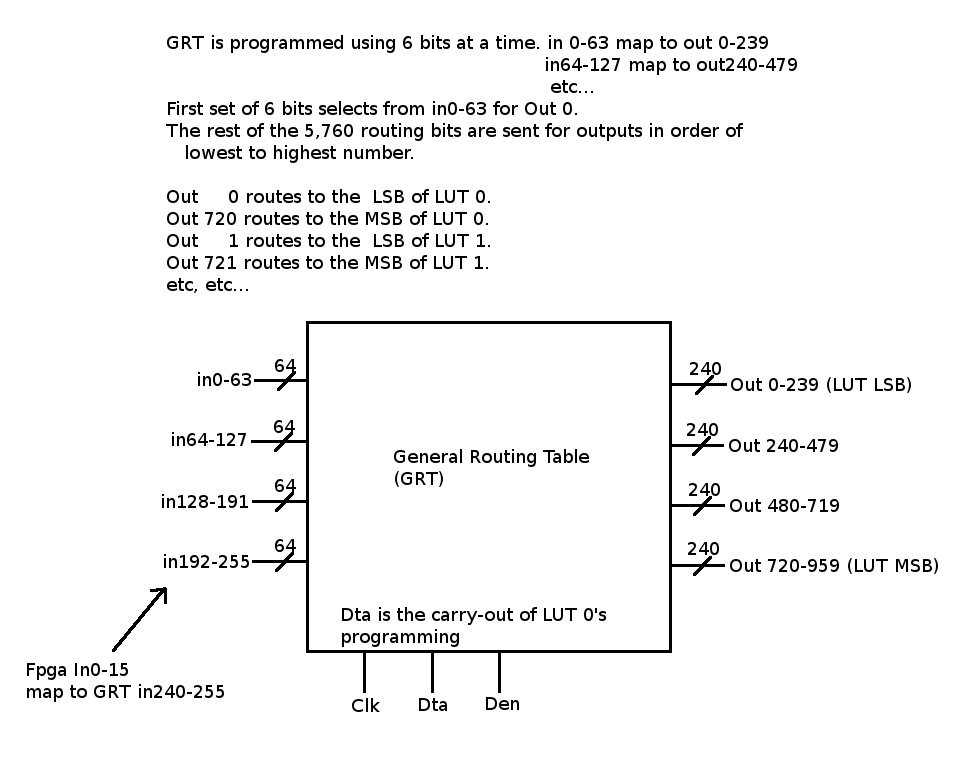

The GRT is programmed 6 bits at a time. The first 6 bits sent represent routing one of inputs 0-63 to input 0 on LUT 0. The next six route input 0 on LUT 1. Eventually, after sending 64 groups of 6 bits, you will start over programming routing to input 1 of each LUT, and so on.

The last thing to remember is that when the FPGA is programmed, the routing table needs to be sent its bits before the LUTs recieve theirs. This was an arbitrary decision that the LUTs would come first in the 100,80 bit programming shift register.

The image below shows another way to think about the GRT structure. There are 940 outputs and 256 inputs. The inputs divide into 4 groups, and the outputs do the same. Inputs in group 0 only route to outputs in group 0. same with 1, 2, and 3.